# An ultrafast front-end ASIC for APD array detectors in X-ray time-resolved experiments\*

Yang-Fan Zhou(周杨帆)<sup>1;1)</sup> Qiu-Ju Li(李秋菊)<sup>1</sup> Peng Liu(刘鹏)<sup>1</sup> Lei Fan(樊磊)<sup>2</sup> Wei Xu(徐伟)<sup>1</sup> Ye Tao(陶冶)<sup>1</sup> Zhen-Jie Li(李贞杰)<sup>1;2)</sup>

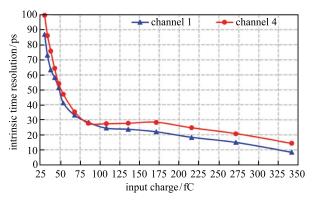

Abstract: An ultrafast front-end ASIC chip has been developed for APD array detectors in X-ray time-resolved experiments. The chip has five channels: four complete channels and one test channel with an analog output. Each complete channel consists of a preamplifier, a voltage discriminator and an open-drain output driver. A prototype chip has been designed and fabricated using 0.13  $\mu$ m CMOS technology with a chip size of 1.3 mm  $\times$  1.9 mm. The electrical characterizations of the circuit demonstrate a very good intrinsic time resolution (rms) on the output pulse leading edge, with the test result better than 30 ps for high input signal charges (>75 fC) and better than 100 ps for low input signal charges (30–75 fC), while keeping a low power consumption of 5 mW per complete channel.

Keywords: time-resolved, APD, ASIC, synchrotron X-ray

**PACS:** 07.85.Qe, 07.50.Ek, 29.40.Wk **DOI:** 10.1088/1674-1137/41/6/066101

#### 1 Introduction

Silicon avalanche-photodiode (APD) detectors have a number of advantages, such as high count rate, large dynamic range, and nanosecond or faster time resolution. They have been used in time-resolved experiments with pulsed synchrotron X-rays, such as nuclear resonance scattering (NRS) experiments [1, 2] and laser pump/X-ray probe experiments [3], for more than two decades. However, traditional time-resolved APD detectors [4–8] only have a single APD sensor and adopt a commercial circuit or discrete element circuit to read out the weak signal output by the APD sensor. In order to acquire a larger reception solid angle, higher count rate and higher integration density, it is necessary to develop an APD array detector for X-ray time-resolved experiments.

We are now developing an APD array detector for the High Energy Photon Source Test Facility (HEPS-TF) project. This is an R&D project for the planned future High Energy Photon Source (HEPS) in Beijing, China. The goal of the detector design is as follows. To get an active area of 1 cm<sup>2</sup>, the array size is  $10 \times 10$ , with a pixel size of 1 mm  $\times$  1 mm. The pixel has a reachthrough structure and the absorption layer thickness is

about  $100 \mu m$ . So the time resolution of the detector, the full width at half maximum (FWHM), can be of the order of 1 ns, corresponding to a root mean square (rms) resolution of 0.426 ns. Ten CMOS ASICs (ten channels each) will be used to read out the pixel array signals.

This paper presents a prototype ASIC chip for the APD array detector. The prototype chip includes five channels: four complete channels and one test channel with an analog output. Each complete channel consists of a preamplifier, a voltage discriminator and an opendrain output driver. The readout noise and the power consumption are reduced by using a flipped voltage follower (FVF) as the input stage of the preamplifier. An AC coupling circuit is also employed in the preamplifier to decrease the DC offset of the preamplifier. The discriminator is based on a cascade of four low-gain and high bandwidth differential amplifiers with a hysteresis function. To match the LVDS output levels, an opendrain differential circuit is adopted as the output driver, which can configure the output level by programming external resistors. The detailed design of the prototype ASIC chip will be discussed in the following sections. Measurement results are also presented to demonstrate the capabilities of the chip. In the next step, a practical

Beijing Synchrotron Radiation Facility, Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China

State Key Laboratory of Particle Detection and Electronics, Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China

Received 4 February 2017

<sup>\*</sup> Supported by the National Natural Science Foundation of China (11605227), High Energy Photon Source-Test Facility Project, and the State Key Laboratory of Particle Detection and Electronics. This research used resources of the BSRF.

<sup>1)</sup> E-mail: zhouyf@ihep.ac.cn

<sup>2)</sup> E-mail: lizj@ihep.ac.cn

<sup>©2017</sup> Chinese Physical Society and the Institute of High Energy Physics of the Chinese Academy of Sciences and the Institute of Modern Physics of the Chinese Academy of Sciences and IOP Publishing Ltd

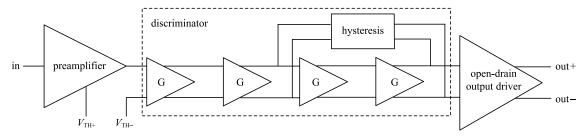

Fig. 1. Functional block diagram for one full channel of the ASIC chip.

ASIC chip with ten channels will be designed based on this prototype chip.

# 2 Design of the readout ASIC

In the five-channel prototype ASIC, four channels have complete functional modules for time measurement and one channel is designed for testing, with the output signal of preamplifier directly exported by an analog driver. Figure 1 shows the block diagram of one full channel. The signal path includes the preamplifier, discriminator and open-drain output driver. The preamplifier receives the current signal, output by the APD sensor, and converts it into a voltage signal. Then, the voltage signal is discriminated by the discriminator. If the voltage signal is larger than the threshold voltage, the discriminator will output a digital pulse. Finally, the digital pulse is output by the open-drain output driver with LVDS levels. Moreover, the whole chip uses a common threshold voltage, which is supplied by an off-chip module.

#### 2.1 Preamplifier

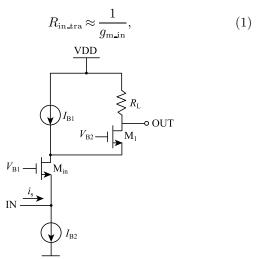

The input stage of a traditional preamplifier [9–11] is shown in Fig. 2. The input resistance of the traditional preamplifier can be calculated as

Fig. 2. Simplified schematic of the input stage of a traditional preamplifier.

where  $g_{\text{m\_in}}$  is the transconductance of  $M_{\text{in}}$ .

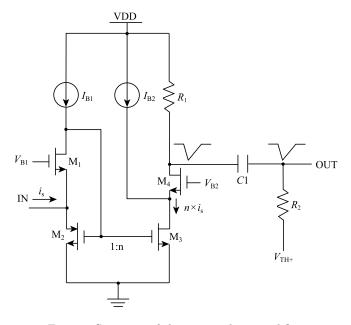

Figure 3 shows the proposed preamplifier structure. The input stage of the preamplifier, constituted by the transistors  $M_1$ ,  $M_2$  and the current source  $I_{B1}$ , is used to receive the APD current signal  $i_s$ . The transistors  $M_1$  and  $M_2$  form a flipped voltage follower (FVF) [12], whose bias current is generated by  $I_{B1}$ . The feedback in the FVF results in a very low input resistance at the input terminal. The input resistance of the preamplifier can be calculated approximately using the following equation [12], and is of the order of a few tens of ohms:

$$R_{\text{in\_amp}} \approx \frac{1}{g_{\text{m1}}g_{\text{m2}}r_{\text{o1}}},\tag{2}$$

Fig. 3. Structure of the proposed preamplifier.

where  $g_{\text{m1}}$  is the transconductance of  $M_1$ ,  $r_{\text{o1}}$  is the output resistance of  $M_1$ , and  $g_{\text{m2}}$  is the transconductance of  $M_2$ . If  $R_{\text{in\_tra}} = R_{\text{in\_amp}}$ , from Eq. (1) and Eq. (2), we can derive that  $g_{\text{m1}} = \frac{g_{\text{m\_in}}}{g_{\text{m2}}r_{\text{o2}}}$ . The dominating noise source in the traditional preamplifier is the thermal noise from the common-gate transistor  $M_{\text{in}}$ , and the dominating noise

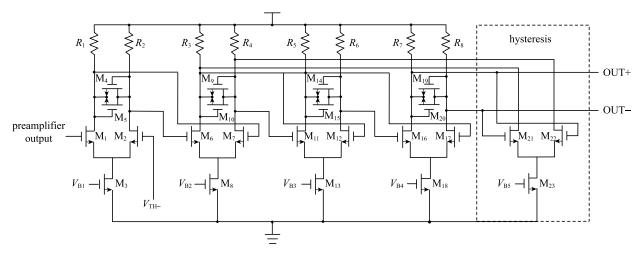

Fig. 4. Structure of the discriminator.

source in the proposed preamplifier is the thermal noise from the common-gate transistor  $M_1$ . The thermal current noise of a MOS transistor decreases with as its own transconductance  $(g_{\rm m})$  decreases [13]. Therefore, the proposed preamplifier has a lower noise performance and can detect a smaller signal than the traditional preamplifier. The transistors M<sub>2</sub> and M<sub>3</sub> compose a current mirror with a gain of n (in this design n=6). After being amplified by the current mirror, the signal-to-noise ratio (SNR) will be sufficiently large to make the preamplifier noise non-critical. The amplified current signal  $n \times i_{\rm s}$  flows through the branch made of transistor M<sub>4</sub> and load resistance R<sub>1</sub>, and is converted into the voltage signal. The bias current of  $M_3$  is provided by the current source  $I_{\rm B2}$ , as a result of which  $I_{\rm B2} \approx n \times I_{\rm B1}$ . The capacitance C<sub>1</sub> and resistance R<sub>2</sub> constitute an AC coupling circuit. In the stationary state the baseline of the preamplifier is kept at the positive threshold  $V_{\text{TH+}}$ , so the DC offsets between the preamplifiers are eliminated. Using the AC coupling technique to fix the baseline is simpler and easier to implement than the feedback baseline restore technique in Refs. [9–11]. The AC coupling baseline holder makes it possible to set a precise threshold for the subsequent discriminator, which is a key point to discriminate the X-ray photon accurately.

#### 2.2 Discriminator

Figure 4 shows the structure of the discriminator. The discriminator is based on a cascade of four low gain and high bandwidth differential amplifiers with resistance loads and diode-connected transistors. The diode-connected transistors are adopted to clamp the output voltages of the differential amplifiers so that the discriminator recovery time from large signals can be reduced. Besides, the amplifier (composed of transistors  $M_{21}$ ,  $M_{22}$  and  $M_{23}$ ) is used in a positive-feedback loop connection and introduces a hysteresis feature for the transition time

to prevent oscillations. The discriminator is optimized for high speed, so relatively small transistors are used. One input of the discriminator is driven from the output of the preamplifier, while the other is connected to the negative threshold  $V_{\rm TH-}$ . The discrimination threshold  $V_{\rm TH}$  is defined as  $V_{\rm TH} = V_{\rm TH+} - V_{\rm TH-}$ .  $V_{\rm TH+}$  and  $V_{\rm TH-}$  are set through the external references, in such a way that all channels have the same threshold value.

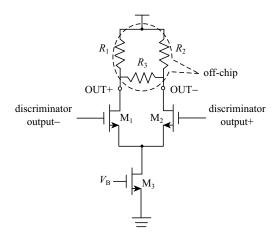

#### 2.3 Output driver

Figure 5 shows the structure of the output driver. The output stage is an open-drain differential circuit which can provide large current switching between the two outputs and output fast leading edge signals. The resistances  $R_1$ ,  $R_2$  and  $R_3$  constitute the external resistance net. We can programme the external resistance net to match the output signal to the user needs. Meanwhile, the output driver is still biased by this resistance net. In the default configuration the differential output signals comply with the LVDS protocol.

Fig. 5. Structure of the output driver.

#### 3 Implementation and measurement

A five-channel prototype ASIC chip was implemented in a 0.13  $\mu m$  CMOS process. Figure 6 shows a photograph of the fabricated ASIC chip. The chip size is 1.3 mm  $\times$  1.9 mm. For convenience of measurement, the readout ASIC chip is wire bonded to a printed circuit board (PCB), which can be connected to an evaluation board through the sockets. Ceramic packaging will be used to package the finalized chip in the future.

Fig. 6. (color online) Photograph of the ASIC chip.

### 3.1 ASIC chip measurement

The signal shape from several APDs for nuclear resonant scattering experiments can be found from Ref. [8]. The leading edge transition time of the APD output signals is from 0.8 ns to 2.1 ns. To capture this fast signal, the time constant at an input node of the ASIC chip should be in the order of a few hundreds of picoseconds. The maximum sensor capacitance in our R&D project is 10 pF. If the ASIC input impedance is 50  $\Omega$ , the RC time constant of the input node is 10 pF×50  $\Omega$ =500 ps, which results in a sufficient bandwidth to receive the APD output signal. Therefore, our ASIC chip is designed with an input impedance of 45  $\Omega$ . However, the APD sensor does not require impedance matching ( $\sim$  50  $\Omega$ ). For this ASIC, no external resistors are used to adjust the actual input impedance.

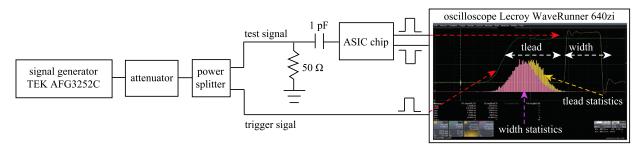

The time measurement setup is shown in Fig. 7. The performance of the ASIC chip was evaluated by generating input current pulses, via applying voltage steps to

the 1 pF injection capacitances integrated in the test board. First, the generator signal was attenuated by an attenuator. Then, this attenuated signal was divided by a power splitter. One signal was connected through an injection capacitance to the input pad of each channel as the test signal, and the other was the trigger signal. To guarantee the impedance matching to the power splitter, 50  $\Omega$  resistances were added in the input terminals of each injection capacitance [14]. A TEK AFG3252C signal generator was used to generate the step voltage signals with a rise time of 2.5 ns. The time differences between the trigger signal and the leading edge of each channel output signal and the pulse width of each channel output signal were recorded and analysed by a Lecroy WaveRunner 640 zi oscilloscope. For each channel, measurements were carried out for different test signal amplitudes, set using different attenuations from the attenuator. For each channel and for each input charge level, 1000 measurements of the output signals were recorded.

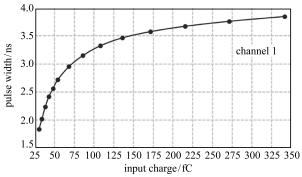

The output pulse width variations with respect to the input charge measured with the threshold ( $V_{\rm TH}$ ) setting at 25 mV are shown in Fig. 8 for channel 1. The typical pulse width varyied from 1.8 ns to 3.8 ns for input charges from 30 fC to 342 fC, respectively. The charge information can be retrieved from the measurement curve of the output pulse width. This curve has a non-linear relation, and a maximum sensitivity for the lower charges is also observed. In order to efficiently use the charge encoding possibilities of the chip with an optimum resolution, the threshold level of the chip must therefore be tuned so as to maximize the sensitivity around the working point of a specific application.

In the case of leading-edge discrimination, the channel output pulse leading edge time  $t_{\rm lead}$  is delayed by the time needed for the signal to reach the threshold value. This delay, the Time Walk  $t_{\rm w}$ , has to be corrected for. The event time  $t_{\rm event}$  can be given by [10, 11]:

$$t_{\text{event}} = T_{\text{lead}} - t_{\text{w}}(V_{\text{TH}}) = t_{\text{lead}} - f(t_{\text{width}}, V_{\text{TH}}), \tag{3}$$

Fig. 7. (color online) Schematic of the setup for chip time measurement.

Fig. 8. Measured pulse width as a function of applied input charge for channel 1, with a threshold of  $25~\mathrm{mV}$ .

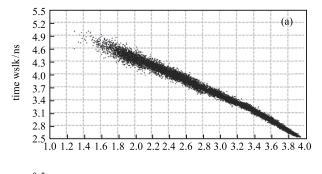

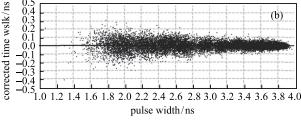

where  $t_{\text{width}}$  is the channel output pulse width. This method, applied off-line, permits a high-time resolution even for input signal amplitude varying on a large dynamic scale. All the  $t_{\text{lead}}$  time measurements acquired for the different input charges on channel 1 are shown in a scatter plot in Fig. 9(a) as a function of the measured pulse width. For the measurement, the threshold is set at 25 mV. The time walk variations are contained in clusters of less than 3 ns for input charges varying from 30 fC to 342 fC. The pulse width measurement can thus be used to correct for the time walk. This time walk correction procedure was applied event by event, leading to the scatter plot shown in Fig. 9(b). For each cluster of data points, the variations now correspond to the uncertainty in the time information that can be expected for a signal with such input charge.

Fig. 9. (a) Measured time walk on the output pulse leading edge versus measured pulse width for channel 1; (b) time walk after off-line corrections applied to compensate variations of time walk with pulse width for channel 1.

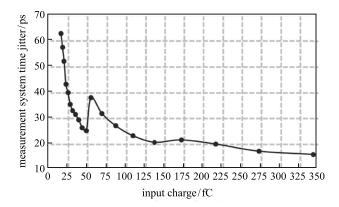

To estimate the intrinsic time resolution of the circuit, the additional noise from the pulse generator and oscilloscope also has to be corrected. The measurement system time jitter has been measured with input charge from 15 fC to 342 fC, as shown in Fig. 10. This curve permits us to extract the function relating measurement system time jitter and input charge, and realize the measurement system time jitter correction procedure.

Fig. 10. Measurement system time jitter.

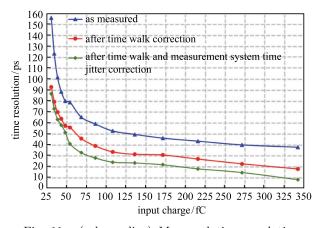

The measured time resolution (rms), the time resolution (rms) determined after time walk correction and the time resolution (rms) after both time walk correction and correction of the measurement system additional jitter noise are presented in Fig. 11 for channel 1, with  $V_{\rm TH}$  set at 25 mV. The excellent time-resolution measured for an input charge Q can therefore be perfectly retrieved in the case of a system involving input signals varying on a large dynamic scale.

Fig. 11. (color online) Measured time resolution (rms) for channel 1, with threshold set at 25 mV, comparing measured time resolution, time resolution after time walk correction, and time resolution after both time walk and measurement system jitter noise correction.

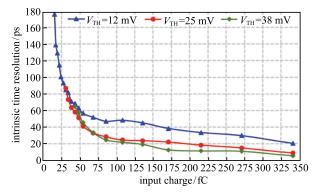

After corrections are applied to compensate for the additional noise from the measurement system and to correct for the time walk variations due to pulse width variations, the intrinsic time resolution (rms) of channel 1 with specified threshold values is displayed in Fig. 12. Achievable resolutions are therefore directly dependent on the threshold level, which should be set according to the input signal shape, amplitude and dynamic range in the application.

Fig. 12. (color online) Intrinsic time resolution (rms) of channel 1 versus input charge for the specified threshold values.

The intrinsic time resolutions (rms) attained at threshold level of 25 mV for channel 1 and channel 4 are shown in Fig. 13. The low charge signals exhibit a higher time uncertainty than signals with a higher charge. The intrinsic time resolution (rms) is better than 30 ps for high input signal charges (>75 fC) and better than 100 ps for low input signal charges (30–75 fC). The ASIC chip performance is detailed in Table 1. The measurement results demonstrate that the prototype chip has reached the design specifications.

# 3.2 Measurement with APD array sensor

Our APD array sensor is being designed by another group. Therefore, the prototype chip has been tested with a commercial APD array sensor (model: S8550-02,

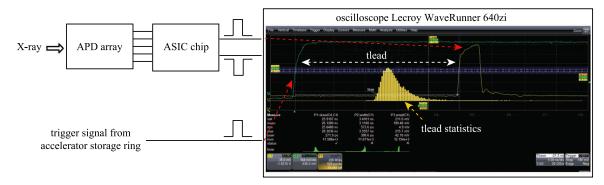

fabricated by Hamamatsu) at the 1W2B experiment station of Beijing Synchrotron Radiation Facility (BSRF). The S8550-02 is a monolithic  $8\times 4$  pixel structure with a photosensitive area of  $1.6~\mathrm{mm}\times 1.6~\mathrm{mm}$  and a terminal capacitance of 9 pF for each pixel. Five of the pixels were connected to the chip. The time measurement setup of the complete detector with sensor and readout chip is shown in Fig. 14. The RF signal from the accelerator storage ring served as the trigger signal. The time differences between the trigger signal and the leading edge of each channel output signal were recorded and analysed by a Lecroy WaveRunner 640zi oscilloscope. All the detector measurements were done with a threshold level set at 25 mV and an APD gain of 50.

Fig. 13. (color online) Intrinsic time resolution of channel 1 and channel 4 for a threshold value of 25 mV.

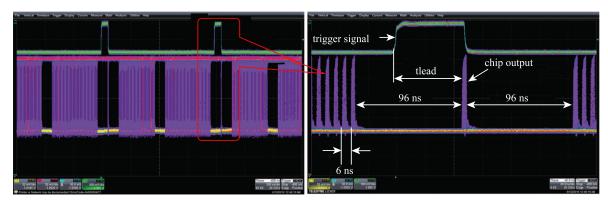

The measured time structure of the beam bunches of BSRF using the developed APD array detector is presented in Fig. 15. The beam bunch structure has a hybrid fill pattern in which a specific single bunch is filled at a sufficient interval from other bunches. This single bunch is used to measure the time resolution of the developed detector. The measured bunch structure is consistent with the bunch current structure from the bunch current monitor, and proves the detector can work in a healthy state.

Table 1. Main performances of the prototype ASIC chip.

| parameter               | performance                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------|

| process                 | 0.13 μm CMOS                                                                                         |

| power consumption       | $< 5~\mathrm{mW}$ / channel (excluding the output LVDS driver consumption)                           |

| signal range            | $25450~\mathrm{fC}$ @ $V_\mathrm{TH}$ = $25~\mathrm{mV}$                                             |

| discriminator threshold | $\geqslant$ 12 mV (15 fC)                                                                            |

| time resolution (rms)   | $<\!30$ ps @ input charge $>\!75$ fC; $<\!100$ ps @ 30 fC $\leqslant$ input charge $\leqslant 75$ fC |

| count rate              | $> 1.2 \times 10^8/\mathrm{s}$                                                                       |

| input resistance        | $\sim 45~\Omega$                                                                                     |

Fig. 14. (color online) Schematic of the setup for detector time measurement.

Fig. 15. (color online) Time structure of the beam bunch at BSRF: hybrid bunch structure with a singlet bunch.

The measured time resolution of the detector at 14.4 keV (equal to 32 fC input charge with the APD gain of 50) is displayed in Fig. 16. The time resolution (FWHM) is 350 ps, without any corrections. The S8550-02 is a "reverse type" APD [15, 16]. As compared with the reachthrough design, the gain region is moved up to the front so that the active thickness is drastically reduced, while

300 250 200 150 100 50 25.8 26.0 26.2 26.4 26.6 26.8 27.0 27.2 27.4 27.6 time/ns

Fig. 16. (color online) Time resolution of the APD detector, with a threshold set at 25 mV.

the depletion layer thickness is kept large. This makes the device specifically suited to couple with scintillators. It is not suitable to directly detect high energy X-rays. In the next step, our designed "reach-through type" APD array will be connected to the ASIC chip to form a practical detector for direct detection of high energy X-rays.

## 4 Summary

In this paper, we have developed an ultrafast frontend ASIC chip for APD array detectors in X-ray time-resolved experiments. The present chip was fabricated in a 0.13  $\mu$ m CMOS process, with four complete channels and one test channel, and fitted in an area of 1.3 mm $\times$  1.9 mm. Pulse width measurement was used to do input charge measurement as well as time walk correction. After both time walk and measurement system jitter noise corrections, an intrinsic time resolution (rms) better than 30 ps for high input signal charges (>75 fC) and better than 100 ps for low input signal charges (30–75 fC) was achieved. The minimum detection threshold can be set at 12 mV, which is equivalent to an input charge

of 15 fC. The power consumption per channel is 5 mW, excluding the LVDS compatible output driver. A preliminary measurement with an APD array sensor (S8550-02) has also been done and a 350 ps resolution (FWHM), without any correction, was obtained. Further analysis and development to manufacture a practical detector is underway, including design of a  $10 \times 10$  pixel "reachthrough type" APD array and a ten-channel ASIC chip.

The authors would like to thank Professor Jiyong Zhao and Professor Michael Y. Hu of Advanced Photon Source, Argonne National Laboratory, for their help in the understanding of the nuclear resonance scattering experiments. The authors would also thank Professor Xiaoshan Jiang and Associate Professor Wei Wei from State Key Laboratory of Particle Detection and Electronics, Institute of High Energy Physics, for their help in circuit design and simulation.

#### References

- 1 G. V. Smirnov, Hyperfine Interactions, 97: 551–588 (1996)

- 2 Makoto Seto, J. Phys. Soc. Jpn, 82: 021016 (2013)

- 3 Da-Rui Sun, Guang-Lei Xu, Bing-Bing Zhang et al, J. Synchrotron Rad, 23: 830–835 (2016)

- 4 Shunji Kishimoto, Rev. Sci. Instrum, **66**: 603–605 (1995)

- 5 Shunji Kishimoto, J. Synchrotron Rad, 5: 275–279 (1998)

- 6 A. Q. R. Baron, Nucl. Instrum. Methodes Phys. Res. A, 343: 517–526 (1994)

- 7 A. Q. R. Baron, R. Rüffer and J. Metge, Nucl. Instrum. Methodes Phys. Res. A, 400: 124–132 (1997)

- 8 A. Q. R. Baron. Hyperfine Interactions, **125**: 29–42 (2000)

- 9 F. Anghinolfi, P. Jarron, F. Krummenacher et al, IEEE Transactions on Nuclear Science, **51**: 1974–1978 (2004)

- M. Despeisse, F. Powolny, P. Jarron et al, IEEE Transactions on Nuclear Science, 58: 202–208 (2011)

- 11 M. Ciobanu, N. Herrmann, K. D. Hildenbrand et al, IEEE Transactions on Nuclear Science, 61: 1015–1023 (2014)

- 12 Ramón González Carvajal, Jaime Ramírez-Angulo, Antonio J. López-Martín et al, IEEE Transactions on Circuits and Systems I: Regular Papers, 52: 1276–1291 (2005)

- 13 Sarpeshkar, Rahul, Tobias Delbruck, and Carver A. Mead, IEEE Circuits and Devices Magazine, 9: 23–29 (1993)

- 14 X. Zhou, Z. Deng, Y. Wang et al, Journal of Instrumentation, 9: C10040 (2014)

- 15 J. Kataoka, T. Saito, Y. Kuramoto et al, Nucl. Instrum. Methodes Phys. Res. A, 541: 398–404 (2005)

- 16 A. Nassalski, M. Moszynski, A. Syntfeld-Kazuch et al, Application of Hamamatsu S8550 APD array to the Common PET/CT Detector, 2007 IEEE Nuclear Science Symposium Conference Record, Hawaii, USA, Oct. 27–Nov. 3, 2007